| 完全な2速システム |  |

| 粗い/細かいチャネルのプログラム可能な速度比 | |

| 1:8、1:16、1:32、1:64 | |

| トライステートラッチ付きデジタル出力 | |

| 最大解像度は20ビットです | |

| 最大精度は5秒角です |

| 粗い/細かい双方向シンクロからデジタルへのコンバーターまたはリゾルバーを含む |

|

| 2人が必要とするデジタルコンバータとエラー訂正論理回路 |

シリーズHTS20製品の粗い/細かい組み合わせの速度比は次のとおりです。 | 1:8、1:16、1:32、1:64、必要な速度比は次の式で得られます。 | 外部プログラム。使い勝手が良いです。双方向の粗い/細かい入力 信号は、3線式シンクロまたは4線式レゾルバの信号です。 シリーズHTS20プログラマブル2スピードSDC/RDCコンバータ出力ナチュラル | 並列バイナリコード。最大は最大20ビットです。彼らはスリーステートを持っています | ラッチ。 | |

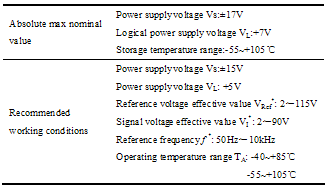

4シンクロからデジタルへのコンバーターの技術仕様または | レゾルバからデジタルコンバータへHTS20シリーズプログラマブル2スピードSDC/RDC | ||||

コンバーター (タブ2、タブ3) | 表2公称条件と推奨される動作条件 *はオーダーメイド可能であることを意味します。 表3電気的特性 特徴 条件 | - - - - | 17 18 19 20 | HTS20R / HTS20S | |

ビジネスの軍事基準 | (Q / HW30925-2006) 単位 コメントコメント 最小 マックス | - - - - | 40 20 10 5 | 解像度 | |

(オプションでSC1、SC2によって制御されます) 速度比 1:8 1:16 | 1:32 - - - | - 50 2 2 | 36 1:64 少し 90 | 精度(0°〜360°) Hz V V | |

|  |

10k 115 | |

,

, レゾルバからデジタルコンバータへHTS20シリーズプログラマブル2スピードSDC/RDC

レゾルバからデジタルコンバータへHTS20シリーズプログラマブル2スピードSDC/RDC コンバーター(図2、図3)

コンバーター(図2、図3) ,

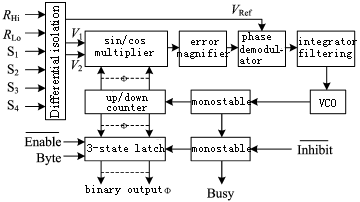

, (1)シングルスピードコンバーター

(1)シングルスピードコンバーター シングルスピードコンバータの動作原理を図2に示します。原理は次のように要約されます。

シングルスピードコンバータの動作原理を図2に示します。原理は次のように要約されます。 ここで、θはアナログ入力角度です。

ここで、θはアナログ入力角度です。 ,

, 2つの信号に内部上下のデジタル角度φを掛けます

2つの信号に内部上下のデジタル角度φを掛けます .

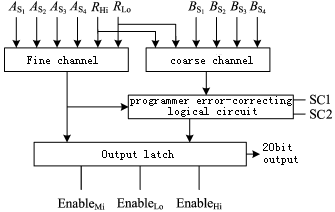

.2速コンバータの動作原理を図3に示します。ザ | 2速コンバータの粗いチャネルと細かいチャネルの動作は |

|  |

| 上記のシングルスピードと同じですが、2スピードコンバーターは シングルスピードコンバーターとプログラマーエラー論理の2セット 回路。粗いチャネルは10〜12ビットの論理角度からの変換を実行します | |

デジタル角度への角度。粗いチャネルによって変換されたデジタル角度と | ファインチャンネルはプログラマーのエラー訂正論理に入力されます | それぞれ回路。エラー処理と修正後、 | 出力に入力される20ビットの2進数を出力します。 | ラッチしてバッファリングしてデジタル角度を出力し、全体を満たします | 変換。 | |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 | 図2機能ブロック図 図3機能ブロック図 シングルスピードコンバーターの (3)データ転送方法とタイミング シリーズHTS202速コンバータの出力は20ビットに達します。終えた と 出力ラッチを3状態制御する2速コンバータは、データバスに簡単に接続できます。 と T1 T2 すべて低レベルで有効です。 EnableLoは下位8ビットを制御し、EnableMiは中間8ビットを制御し、EnableHiは残りの上位ビットを制御します。 シリーズHTS202速コンバータのデータは次のように読み取られます。 セットする 論理「0」に、490μm後、コンバータのトライステートラッチのデータは アップグレードされました。下位8ビット、中位8ビット、上位ビットのデータを読み取ることができます 制御することによって と 図42速コンバータと8ビットデータバスが接続されている場合のデータ読み取りのタイミングを示します。 2速コンバータの高精度変換を確保するために、以下の点に注意してください。

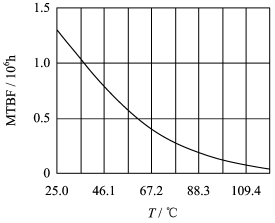

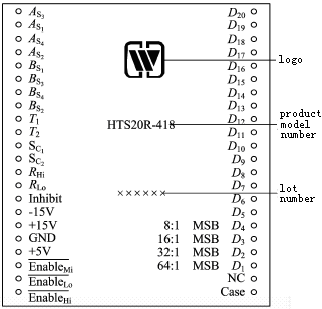

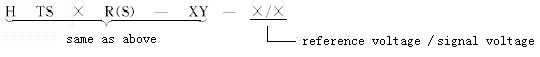

| 粗いチャネルと細かいチャネルの入力信号の振幅は、公称値の10%以内で保証する必要があります。 粗いチャネルと細かいチャネルの入力信号と基準信号の周波数は、指定された動作周波数である必要があります。 粗い入力信号と基準信号間の位相シフト ファインの入力信号と参照信号の間のチャネルと位相 チャネルは10°未満である必要があります。 粗いチャネルと細かいチャネルの入力信号と基準信号の波の歪みは5%未満である必要があります。 + 5V、±15V電源の変動は±5%以内で保証されるべきです。 6シンクロからデジタルへのコンバータのMTBF図または レゾルバからデジタルコンバータへHTS20シリーズプログラマブル2スピードSDC/RDC コンバーター(図5) シンクロからデジタルへのコンバーターの7つのピン構成または レゾルバからデジタルコンバータへHTS20シリーズプログラマブル2スピードSDC/RDC コンバーター(図6、Tab4) 図5MTBFと温度図6上面図をピンで留める (注:GJB / Z 299B-98によると、 その地面は良好な状態です) 表4ピンの説明 ピン ニモニック 説明 ピン ニモニック 説明 As3 As1 As4 | 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 | As2 NC Bs1 Bs3 Bs4 Bs2 D5 D6 D7 D8 D9 SC1 SC2 RHi RLo 禁止する -15V + 15V GND + 5V ファインチャンネル入力 ファインチャンネル入力 | ファインチャンネル入力 ファインチャンネル入力 粗いチャンネル入力 粗いチャンネル入力 粗いチャンネル入力 粗いチャンネル入力 位相シフト用の調整ピン 信号と参照の間 位相シフト用の調整ピン 信号と参照の間 粗いプログラム制御ピン と細かい速度比 粗いプログラム制御ピン と細かい速度比 リファレンスハイの入力ピン リファレンスローの入力ピン 信号を禁止する -15V入力 +15V入力 接地 +5V入力 中間の8ビットデータを有効にする | |

,

, D10

D10 D11

D11 D12

D12 D13

D13 D14

D14

接続されていません 最高の結合デジタル角度の出力 | 結合されたデジタル角度の出力 | 結合されたデジタル角度の出力 結合されたデジタル角度の出力 | 結合されたデジタル角度の出力 | 結合されたデジタル角度の出力 結合されたデジタル角度の出力 | 結合されたデジタル角度の出力 |

結合されたデジタル角度の出力 | 結合されたデジタル角度の出力 | 8 | 結合されたデジタル角度の出力 | 15 | 結合されたデジタル角度の出力 |

2 | 結合されたデジタル角度の出力 | 9 | 結合されたデジタル角度の出力 | 16 | 結合されたデジタル角度の出力 |

3 | 結合されたデジタル角度の出力 | 10 | 結合されたデジタル角度の出力 | 17 | 結合されたデジタル角度の出力 |

4 | 結合されたデジタル角度の出力 | 11 | 最小結合デジタル角度の出力 | 18 | ノート: |

5 | HTS20Sのピン3,7は接続されていません。 | 12 | As1、As2、As3、As4はファインチャンネル入力です。シンクロに3線が装備されている場合、As4は使用されません。 | 19 | Bs1、Bs2、Bs3、Bs4は粗いチャネル入力です。シンクロに3線が装備されている場合、Bs4は使用されません。 |

6 | RHi、RLoは基準信号入力です。 | 13 | 禁止は、プルアップ抵抗によって5V電源に接続されている禁止信号です。禁止が論理「0」の場合、内部は禁止されます。 490ns後、有効なデータが出力され、読み取ることができます。論理が「1」の場合、コンバータはトラッキング状態を復元し、出力されたデータは無効なデータです。 | 20 | 禁止する |

7 | と | 14 | 状態を決定するデータ出力の3つの状態制御ピンです |

ケースはケースピンです。

D1〜D20は、結合されたデジタル角度の出力です。 D20は最も重要ではありません

少し。速度比が1:8の場合、D4が最上位ビットになります。スピードが出るとき | 比率は1:16で、D3が最上位ビットです。速度比が1:32の場合、D2 | 最上位ビットです。速度比が1:64の場合、D1が最も | 最上位ビット。 シンクロからデジタルへのコンバーターまたはレゾルバの8ビット重量表 | デジタルコンバータへのHTS20シリーズプログラマブル2スピードSDCまたはRDC コンバーター(タブ5) | 表5ビットウェイトテーブル | 少し | 番号 重量(度) | 少し |

番号 | 重量(度) 少し | 番号 | 重量(度) | 1(MSB) | 180.0000 1.1063 | 0.011(40秒) | 90.0000 |

|

|

| 45.0000 |

X

X