| 内部差動絶縁変換 |  |

| 解像度:16ビット | |

| スリーステートラッチ出力 | |

| データ転送中の中断のない追跡 | |

| 32線式金属パッケージ |

HSDC/HRDC1746シリーズシンクロ/レゾルバ-デジタルコンバーターが設計されています | タイプIIサーボトラッキング原理の原理に基づいて採用 | |||||

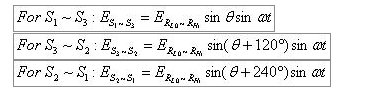

差動絶縁入力、データ出力はスリーステートラッチを採用 | モード、それはのアナログ信号/デジタル信号変換に適しています | 3線式シンクロと4線式レゾルバ。変換速度が速い | 安定した信頼性の高いパフォーマンスで、このデバイスは広く適用できます 角度測定および自動制御システムで。 | この製品は、厚膜ハイブリッド統合プロセスによって製造されており、 | ||

32線式DIP完全密閉金属パッケージ。デザインと | ||||||

製品の製造はGJB2438A-2002の要件を満たしています | 「ハイブリッド集積回路の一般仕様」および特定 | 製品の仕様。 | ||||

4.電気的性能(表2、表3) | シンクロからデジタルへのコンバーターまたはレゾルバからデジタルへのコンバーター(HSDC / HRDC1746シリーズ) | 表2定格条件と推奨動作条件 | 表3電気的特性 | 絶対最大定格値 | ||

供給電圧Vs:±17.25VDC | パラメータ | -3 | 3 | |||

HSDC / HRDC | 1746シリーズ | 16 | ||||

ノート | 論理電源電圧VL:+ 7V | 50 | 保管温度範囲:-55℃〜150℃ | |||

最小 | 最大 | 2 | 90 | |||

推奨動作条件 | 供給電圧Vs:±15±5% | 2 | 精度/角度分 | |||

| 2.6k |  |

| 信号と励起の間の位相シフト:<±10% 信号電圧(実効値)/ V 作動温度範囲(TA):-40〜+105℃  | |

| 基準電圧(実効値)/ V | 115 |

| |

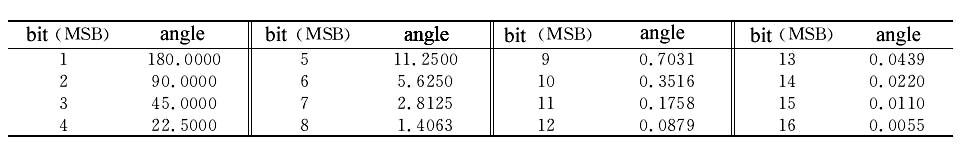

| エラー関数が取得されます: |

エラー増幅、位相弁別、これのフィルタリングを通じてof 誤差関数sin(θ-φ)は、θ-φu003d 0のときに得られます(精度の範囲内 | コンバータの)、このエラーは電圧を制御しますofバイナリデジタル角度φを変更する発振器出力補正パルス |

| |

| 出力φ値が | コンバータの精度内でθを入力すると、システムは安定します |

| 入力角度φの変化を追跡できます。このように、バイナリデジタル | |

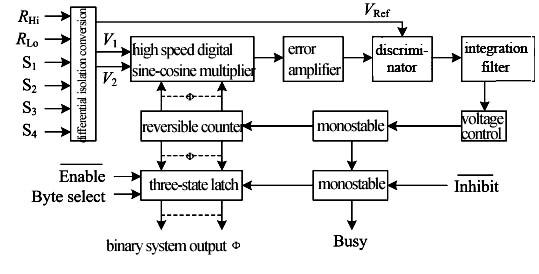

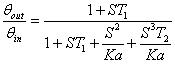

リバーシブルカウンター(図2)。 | 図2回路ブロック図 | (1)動的特性 | コンバータの伝達関数を図3に示します。 | 開ループ利得: | 閉ループ機能: |

1 | NC | このモデルのモジュールの場合、Ka u003d 48000 / S2、T1 u003d 7.1ms、T2 u003d 1.25ms | 17 | NC | 図3コンバータの機能転送 |

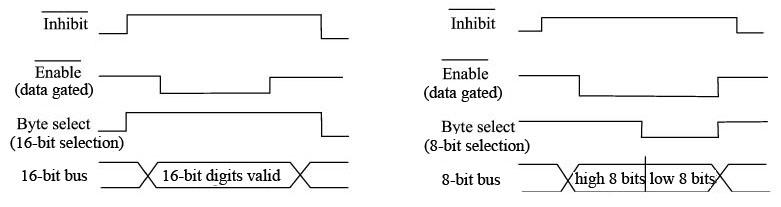

2 | D9 | (2)データ転送の方法と時系列 | 18 | チップセレクト制御有効 | このピンは制御ロジックの入力ピンであり、その機能は出力することです |

3 | スリーステート制御を実現するためのコンバータへのデータ。低レベルは | 有効な場合、コンバータの出力データはデータバスを占有します。にあるとき | 19 | ハイレベルでは、コンバータのデータ出力ピンは3つの状態にあります。 | デバイスはバスを占有しません。 |

4 | バイト選択 | このピンは制御入力ピンであり、その機能は外部で実行することです | 20 | 転送中のコンバータの出力データの選択制御 | 8ビットデータバスまたは16ビットデータバスのモード。 16ビットデータバス転送時 |

5 | モードが必要です。このロジックピンをハイに保つと、データは次のようになります。 | バスに転送され、上位バイトの出力はピンD1からD8にあります(D1は | 21 | 上位ビット)および下位バイトはD9からD16にあります。 8ビットデータバス転送時 | モードが必要な場合、データはピンD1からD8で取得されます(高から配置) |

6 | 〜下位)、および上位8ビットと下位8ビットが2回で取得されます | シーケンス、言い換えると、バイト選択がロジックハイの場合、ハイ8ビット | 22 | が出力され、ロジックローの場合はロー8ビットが出力されます。 | データロック制御(禁止信号)禁止 |

7 | このピンは制御ロジックの入力ピンであり、その機能は出力することです | オプションのラッチまたはバイパスを実現するためのコンバータの外部のデータ | 23 | コントロール。高レベルでは、コンバータの出力データは直接です | ラッチなしで出力します。データの時系列図を参照してください。 |

8 | 移行。低レベルでは、コンバータの出力データがラッチされ、 | 内部ループは中断されず、追跡はすべて機能し続けます | 24 | D1 | 時間ですが、カウンターはデータを出力しません。転送が必要な場合 |

9 | データの場合、コンバータは最初に抑制制御信号を作成してデータをハイからローにロックし、ロジックを640nsの間ローに保ち、次にイネーブル入力をローに設定し(この時点でデバイスはデータバスを占有します)、次に | バイト選択を介してデータを取得し、すべての制御ロジックをハイにします | 25 | D2 | データを更新してラッチし、転送の準備をします。 |

10 | 次のデータは、データ転送の時系列図を参照してください図4 | および図5。 | 26 | D3 | (3)入力信号の減衰方法(図4、図5) |

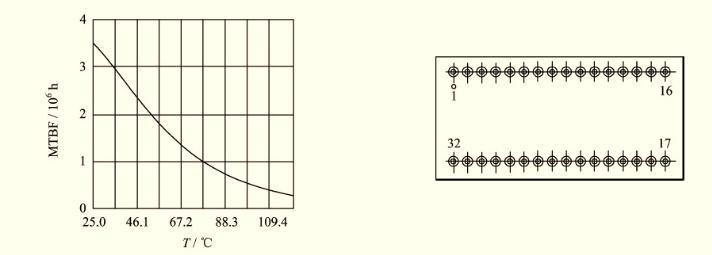

11 | 図416ビットバス転送の時系列 | 図58ビットバス転送の時系列 | 27 | D4 | 6. MTBF曲線(図6) |

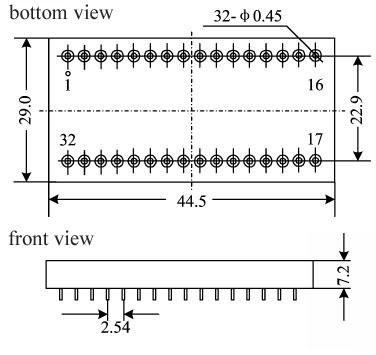

12 | シンクロからデジタルへのコンバーターまたはレゾルバからデジタルへのコンバーター(HSDC / HRDC1746シリーズ) | 7.ピン指定(図7、表4) | 28 | D5 | シンクロからデジタルへのコンバーターまたはレゾルバからデジタルへのコンバーター(HSDC / HRDC1746シリーズ) |

13 | S3 | 図6MTBF-温度曲線 | 29 | D6 | 図7ピン指定(底面図) |

14 | S2 | (注:GJB / Z299B-98によると、良好な地面の状態が想定されています) | 30 | D7 | 表4リード端子の機能説明 |

15 | S1 | ピン | 31 | D7 | シンボル |

16 | NC | 意味 | 32 | NC | ピン |

接地 | D12 | 12ビットのデジタル出力 | -VS | -15V電源 | D13 | 13ビットのデジタル出力 | + VS | +15V電源 |

D14 | 14ビットのデジタル出力 | Ni | 禁止する | Ni | データロックの制御 | D15 | 15ビットのデジタル出力 |

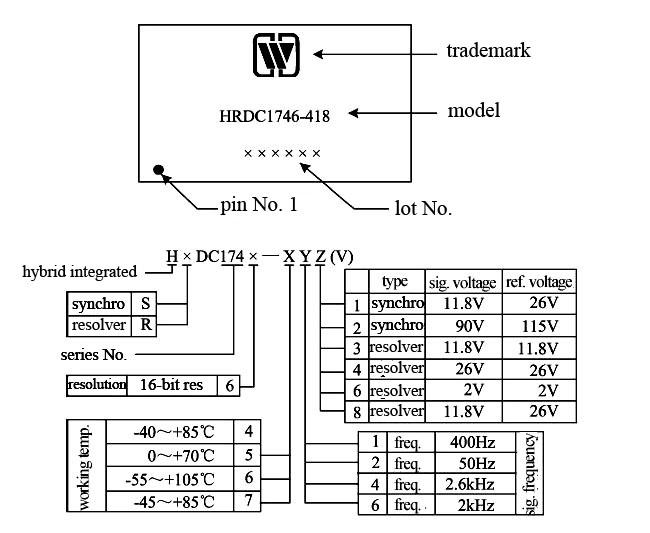

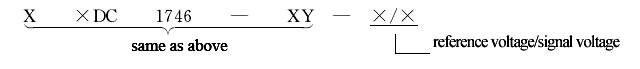

X

X