| 内部差動分離変換 |  |

| 16ビット解像度 | |

| 精度:2角分 | |

| スリーステートラッチ出力 | |

| 高い連続追跡速度 | |

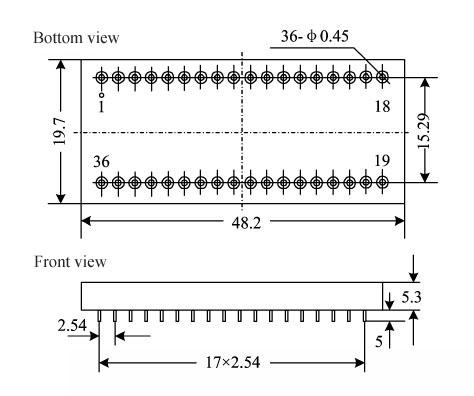

| 36線式耐塩霧金属シールDDIPパッケージ | |

| DDC会社のモデルSDC14560と互換性のあるピンツーピン |

| で設計された連続追跡用の統合変換デバイス | モデルIIサーボの原理。このシリーズの製品は、 |

| MCMプロセスで製造され、コア要素は特別なチップを採用しています | |

| 当研究所が独自に開発しました。ピン配列は | |

| アメリカのDDC社のSDC14560シリーズ製品と互換性があり、16ビット | |

| パラレルナチュラルバイナリコードデータラッチ出力、36ラインDIP完全に | |

| 密封された金属パッケージは、高精度、小型の利点があります | |

| ボリューム、低消費電力、軽量、高信頼性など、 | そして、次のような重要な戦略的および戦術的な武器で広く使用することができます |

| 航空機、海軍艦艇、大砲、ミサイル、レーダー、戦車など。 | |

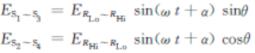

| 4.電気的性能(表1、表2) | |

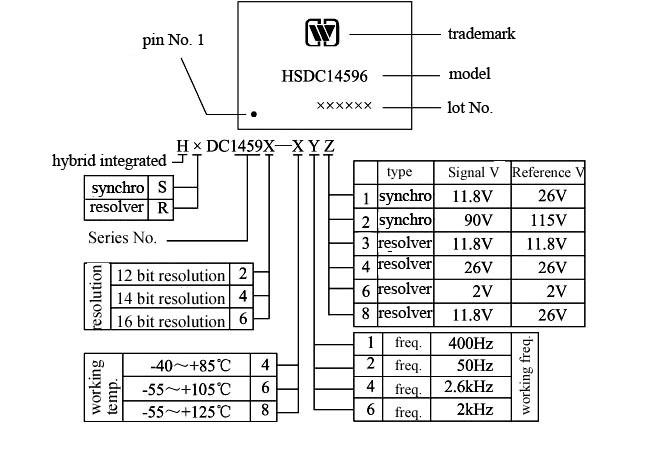

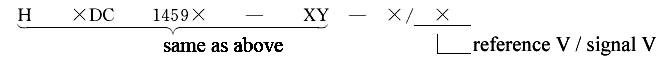

| シンクロからデジタルへのコンバーターまたはレゾルバからデジタルへのコンバーター(HSDC / HRDC1459シリーズ) | |

| 表1定格条件と推奨動作条件 | |

| 絶対最大評価値 |

| 信号電圧V1:定格値±20% | 基準電圧VRef:定格値±20% | 動作周波数f:定格値±20% | |

| 保管温度Tstg:-65〜150℃ | 推奨動作条件 | ||

| 論理電源電圧VL:5±0.5V | 供給電圧Vs:15±0.75V | ||

| 信号電圧V1:定格値±10% | 基準電圧VRef:定格値±20% | 動作周波数f:定格値±20% | — |

| 動作温度範囲(TA):-55℃〜125℃ | 注:*は、ユーザーの要件に応じてカスタマイズできることを示します。 | 表2電気的特性 | パラメータ |

| 条件 | — | HSDC14569シリーズ | (VS u003d 15V、VL u003d + 5V) |

| 軍事標準(Q / HW20725-2006) | — | 2V | 最小 |

| 最大 | — | 解像度 | バイナリシステムのパラレルデジタルコード |

| 16ビット | — | 2V | 正確さ |

| 動作周波数の信号電圧、基準電圧、変動範囲の±10% | — | -2角分 | +2角分 |

| 参照頻度の範囲 | — | 50Hz | 2600Hz |

| 基準電圧の範囲 | — | 115V | 参照入力インピーダンス |

4.4kΩ 4.4kΩ | — | 0 | 129.2kΩ |

信号電圧の範囲 信号電圧の範囲 | — | 0 | 90V |

信号入力インピーダンス 信号入力インピーダンス | — | 0 | 4.4kΩ |

| 102.2kΩ | — | 信号/基準位相シフト | —70° |

| +70° | — | 入力ロジックレベル | ロジック「1」≥3.3V |

| ロジック「0」≤0.8V | — | 入力 | 0.8V |

| 入力 | — | 0.8V | |

| 入力 | — | — | 0.8V |

| 出力ロジックレベル | — | — | ロジック「1」≥3.3V |

| ロジック「0」≤0.8V | — | — | デジタルアングルコード出力 |

| ロジック「1」≥3.3V | — | — | ロジック「0」≤0.8V |

| ビジー信号(CB)出力の変換 | — | 200ns | 600ns |

| 障害検出ビット出力 | ロジック「0」は障害を示します | — | 積載能力 |

| 3TTL | 追跡速度 | ||

| 2.5rps | 加速定数 | ||

| + 10V 現在 VS u003d + 15V 10mA |  VS u003d —15V |

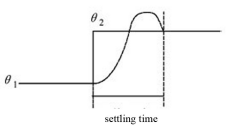

速度。出力デジタル角度の発振プロセスを以下に示します。

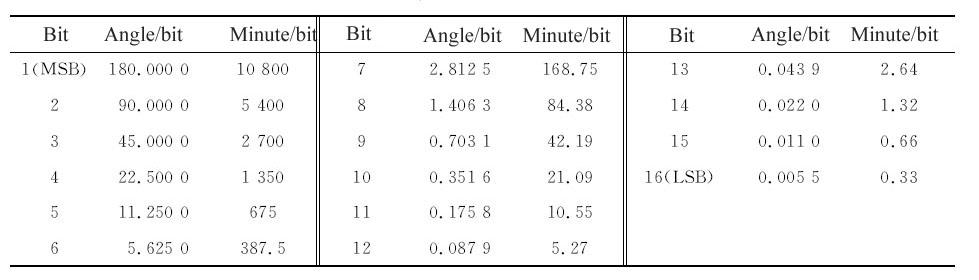

速度。出力デジタル角度の発振プロセスを以下に示します。 6.動作原理(図3)

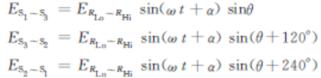

6.動作原理(図3)| シンクロからデジタルへのコンバーターまたはレゾルバからデジタルへのコンバーター(HSDC / HRDC1459シリーズ) シンクロ(またはリゾルバー)の入力信号は、内部の差動絶縁を介して直交信号に変換されます。 | |

Vcos u003d KE0sin(ωt+α)cosθ(cos)ofここで、θはアナログ入力角度です。 図2ステップ応答の曲線 | これらの2つの信号と内部リバーシブルカウンターのデジタル角度φof サイン関数とコサイン関数の乗数で乗算され、 エラー処理: |

| 増幅、位相弁別、統合ろ過( | θ-φ≠0、電圧制御発振器はパルスを出力し、 | の精度内でθ-φがゼロになるまで、可逆カウンターカウント | コンバーター、このプロセス中に、変換はの変化を追跡します | 常に入力角度。 | 読み方: |

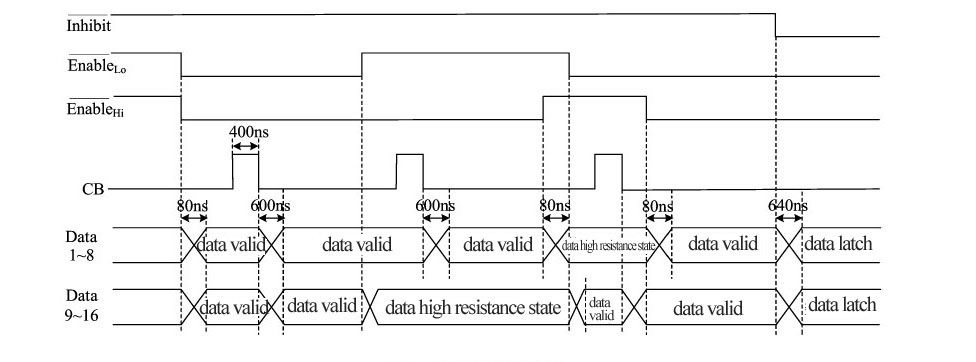

| 1 | S1 | データ転送には、次の2つの方法を使用できます。 | 25 |  | (1)禁止方法: |

| 2 | S2 | 640ns後 | 26 |  | ロジックロー、出力データは有効であり、コンバータはを介してデータ転送を実現します |

| 3 | S3 | と | 27 | 。禁止が解除されると、システムはデータ更新のためにビジーパルスと等しい幅のパルスを自動的に生成します。 | (2)バストモード: |

| 4 | S4 | ビジーパルスの立ち上がりエッジでは、スリーステートリバーシブルカウンターがカウントされます。ビジーパルスの下降エッジで、スリーステートラッチのデータを更新するために、ビジーパルスと等しい幅のラッチパルスを内部で生成します。データ転送の時系列は、図4に示されています。ビジーロジックが低い場合、データの安定した転送が有効です。非同期読み取りモードでは、ビジー出力はCMOSレベルのパルス列です。高レベルと低レベルの幅は、選択したデバイスの動作周波数と回転速度によって異なります。 | 28 | VL | 図4データ転送の時系列 |

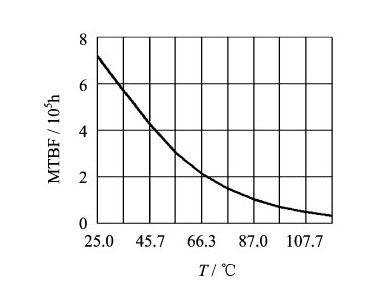

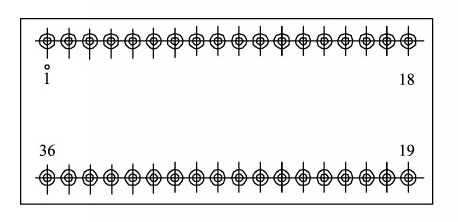

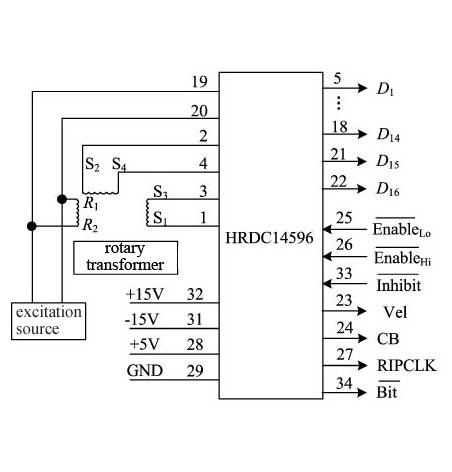

| 7. MTBF曲線(図5) | シンクロからデジタルへのコンバーターまたはレゾルバからデジタルへのコンバーター(HSDC / HRDC1459シリーズ) | 図5MTBF-温度曲線 | 29 | 8.ピンの指定(図6、表3) | シンクロからデジタルへのコンバーターまたはレゾルバからデジタルへのコンバーター(HSDC / HRDC1459シリーズ) |

| 19 | 図6ピンの指定(底面図) | (注:GJB / Z299B-98によると、良好な地盤状態が想定されています) | 30 | NC | 表3ピンの指定 |

| 20 | RL | ピン | 31 | シンボル | 意味 |

| 21 | ピン | シンボル | 32 | VS | 意味 |

| 22 | リゾルバ入力S1(またはシンクロ入力S1) | 下位8ビットのデジタル対応制御 | 33 | リゾルバ入力S2(またはシンクロ入力S2) | 上位8ビットのデジタル対応制御 |

| 23 | リゾルバー入力S3(またはシンクロ入力S3) | RIPCLK | 34 | ゼロビット信号出力 | リゾルバ入力S4(未接続のまま) |

| 24 | CB | +5V電源 | 5月18日 | NC | D1-D14 |

| デジタル出力1(MSB)-14 | GND |

| 接地 | RHi |

| 基準信号入力のハイエンド | 接続なし |

| RL | 基準信号入力のローエンド |

-VS

-VS -15V電源

-15V電源

D15 デジタル出力15

デジタル出力15 ).

).

+15V電源

D16

デジタル出力16(LSB)

禁止する

静的信号入力

ベル

S1、S2、S3、S4

S1、S2、S3、S4

基準信号入力のローエンドof低い | 8ビット桁対応の信号入力。このピンはの論理入力ピンです。ofデータゲーティング制御、その機能はスリーステート制御を実行することです |

|  |

| コンバータの下位8ビット出力データの外部。低レベルは | 有効な場合、コンバータの下位8ビット出力データがデータを占有します |

抵抗状態であり、デバイスはデータバスを占有しません。有効リリース遅延時間は600ns(最大)です。 | より高い | 8ビット桁対応の信号入力。このピンはの論理入力ピンです。 | データゲーティング制御、その機能はスリーステート制御を実行することです | コンバータの上位8ビット出力データの外部。低レベル | が有効な場合、コンバータの上位8ビット出力データがデータバス;ハイレベルでは、上位8ビット出力データのピンがハイになります。 | 抵抗状態であり、デバイスはデータバスを占有しません。有効 | リリース遅延時間は600ns(最大)です。 | 静的を禁止する |

信号入力、このピンは制御ロジックの入力ピンであり、その機能 | オプションを実現するためにコンバーターの外部にデータを出力することです | Niラッチまたはバイパス制御。高レベルでは、の出力データ | コンバーターはラッチせずに直接出力します。低レベルでは、出力 | コンバータのデータはラッチされ、データは更新されませんが、内部ループは中断されず、追跡はすべての | 時間、Inhibitはプルアップ抵抗を内部に接続しました。 600ns(最大)の遅延後 | Au 静的信号の下降エッジで、データは安定します( | デバイスはデータバスを占有します。つまり、データはいつ出力されますか。の状態について | とCB「ビジー」信号出力、この信号はバイナリコードかどうかを示します |

X

X